Product Summary

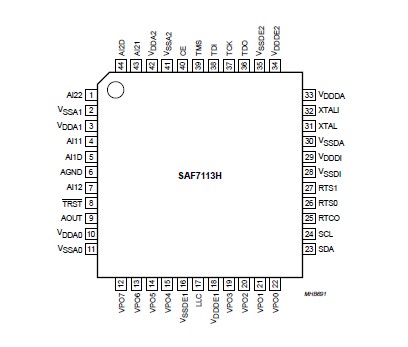

The SAF7113H is a 9-bit video input processor. The SAF7113H is a combination of a two-channel analog preprocessing circuit including source selection, anti-aliasing filter and ADC, an automatic clamp and gain control, a Clock Generation Circuit (CGC), a digital multi standard decoder (PAL BGHI, PAL M, PAL N, combination PAL N, NTSC M, NTSC-Japan, NTSC N and SECAM), a brightness, contrast and saturation control circuit, a multi-standard VBI data slicer and a 27 MHz VBI data bypass; see Fig.1. The pure 3.3 V CMOS circuit SAF7113H, analog front-end and digital video decoder, is a highly integrated circuit for desktop video applications. The decoder is based on the principle of line-locked clock decoding and is able to decode the colour of PAL, SECAM and NTSC signals into ITU-R BT.601 compatible colour component values. The SAF7113H accepts as analog inputs CVBS or S-video (Y/C) from TV or VTR sources. The circuit is I2C-bus controlled.

Parametrics

SAF7113H absolute maximum ratings: (1) VDDD digital supply voltage: -0.5, +4.6 V; (2) VDDA analog supply voltage: -0.5, +4.6 V; (3) ViA input voltage at analog inputs: -0.5, VDDA + 0.5(4.6 max)V; (4) VoA output voltage at analog output: -0.5, VDDA + 0.5 V; (5) VoD output voltage at digital outputs outputs active: -0.5, VDDD + 0.5 V; (6) DVSS voltage difference between VSSA(all) and VSS(all): - 100 mV; (7) Tstg storage temperature: -65 +150 °C; (8) Tamb operating ambient temperature: -40 +85 °C; (9) Vesd electrostatic discharge all pins note 1: -2000 +2000 V.

Features

SAF7113H features: (1) Four analog inputs, internal analog source selectors, e.g. 4 ×CVBS or 2×Y/C or (1×Y/C and 2×CVBS); (2) Two analog preprocessing channels in differential CMOS style for best S/N-performance; (3) Fully programmable static gain or automatic gain control for the selected CVBS or Y/C channel; (4) Switchable white peak control; (5) Two built-in analog anti-aliasing filters; (6) Two 9-bit video CMOS Analog-to-Digital Converters (ADCs), digitized CVBS or Y/C-signals are available on the VPO-port via I2C-bus control; (7) On-chip clock generator; (8) Line-locked system clock frequencies; (9) Digital PLL for horizontal sync processing and clock generation, horizontal and vertical sync detection; (10) Requires only one crystal (24.576 MHz) for all standards; (11) Automatic detection of 50 and 60 Hz field frequency, and automatic switching between PAL and NTSC standards.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

SAF7113H |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

SAF7113H/V1,518 |

NXP Semiconductors |

Video ICs VIDEO INPUT PROCESSR |

Data Sheet |

Negotiable |

|

||||

|

SAF7113H/V1,557 |

NXP Semiconductors |

Video ICs 9-BIT VIDEO INPUT PROCESSOR |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))